module-2. Combinational Log \* Introduction: -At logic circulat is combinational if ill offs at any time are afunction of only the present enputs. eg: All baste gates AND. DR. NOT. and also Décoder: encoder: mux. De mun de \* combinational cruitst \* combinational circuit consiets of an interconnection of logic gates combinational logic, erruit will transfer the binary information from the given imput data to a required output data. A block diagram of a combinational circuit is shown in fight. with a brank table to canned with OKEN Scan

nes de la combinational (molps.) tige Block diagram of combinational circuit. \* The nimput binary variables cometrom an external source. & the m. oleput variables are produced by the input signals along on the internal combinational logic circuit. & go to an enternal destination \* For n. inputs variables. there are 27 possible : combinations of the binary Inputs. mapping a da ba \* For each possible ilp combination, there is one possible. Value for eath ofp Variable. combinational circuit campe Specified with a touth table. that lists 7 Thus, a

the output Values for each combination op input variables. by americations \* Design procedure2= \* The design of combination ceruits starts from the specification of the design opjective or a set of Boolean f.D.s. from which the togic diagramme can be obtained \* The proceedure involves the following steps. D From the split cation of the cruit, determine the required number of ilps and output & assign a symbol to early. 2) Devine the toath table that defines. the required subationship. blw. Inputs and 3) obtain the simplified Boolean. Jos outputs. for each . 01ps . as a fin of the 1/p Variable.

4) Draw. the logic · diagram and verity the · corrections · of the design (manually or by simulation) \* Lode lonversion Example? \* A conversion circuit must be inserted between the two systems if each-uses different codes for the same information \* Thus a code convertor is a circuit that makes the two systems compatible even though each uses a different benary code let us consider example that converts BCD to the excess-3 code for the decimal digits. separat substant BOD 1000 BOD 100, tooll t<u>0011</u> 1100 A. (100) Encu-3.0011

7 Truth table for code conversion Example Olp. Exich-3 coole Ip BCD W X BCD A 1: 0 D 00 0 D ۰O D  $\bigcirc$ 0 V 0 Ø 0 0 Ø O0 O 0 Ø 0 0 0 Ø P 0 0 0 Ð 0 0 0 0 0 1 0 0 00 0 0 D 1: 0 0 For ርወ ርወ AB 4020 ED ED CD P ¢D CDCD 1000 , AB 0 10 F072 D D 00 ÃE OD ĀB τ 0. 0 C 01 AB01 ŦΒ Ŷ Х AB х AB 11 AB 10 ABLO 2=D 4= CD+CD.

Trackly faller for For X AB CP 210 18 CD 0 ABOD ABOI 0. 0 0 AB 11 X X 000 ABO 0 a' X = BCO + BD + BD-or W FP 60 20 20 AB D Ø AB OO. AB,0 AB 11 ABID X = A+BD+BB BC The expression obtained from each k-map. may be manipulated algebraically for the purpole of using common gates for two or more. Outputs.

Timose Adden - Bullinger

\* The manipulation give flexibility to obtained wifer multiple-output système. when implemented wifes. three or more level · anithorny study priority . of gates. y = c0 + T0 = c0 + (c+0) $\chi = BC+BO+BCO=BCC+D)+BCD$  $\omega = \overline{B}C(t+D) + B(c+D)$ w = A + BC + BP = A + B(C + D)Structo stand of the CD' 319114 % (e+D)B(IN)? BICTO . and Hearit. bit of the Logte diagram. for BCO-to Excess-3 code convertes.

\* Binary Adder - Subtractor:-\* Digital computes perform avariety of Information-processing tasks. \* Among the functions encontered are the various · arithmatic · operations. \* The most basic orithmetic operation is the addition of two binary digits. \* This simple addition consists of four possible elementary operations: oto=0 ot1=1, 1+0=1 & 1+1=10. \* Here first three operations produce a Sumof one digit but when both augent and addend bits are equal to 1, the binary- sum consists of two dogits. -> The higher Stoppificant bit of this refult is called is a carry. E RECH S CORE COMVERS

Scanned with OKEN Scanner

A combination circuit. A that performs the addition of two bits. is called a half adder. I one that perform the addition of three bits. is a full-addes. 27 20 ACTING C DIPLOS \* Half Addes -The SOLD 36178 \* From the verbal explanation of a HA corcuit needs two we find that this binary olps. binary . I ps . 8 two \* The ilp variables designate the augend 8 addend . bits. \* The olp-variables produce the lum. g × let als arsign. symbol. 21 & 4 to the two I/ps . & S. (for secon). & c (for carry). to the pine the Ope. ANG ST

A complimenting SE X Ell adult (m) Ø 0 0 half adda. O 0 K Ene llat peopoons X. D X The C OLP is I only when both. Ilps oren The S OLP. represents the teast sum. \* the simplified. Sum-of-products. AHS expressions ore  $S = \pi y + \pi y$ Variables (='ny A.T. togte diagram. of the HA implemented 21.3 in sop. form is shown bortige the 2. OPPLID. 15 at. (1) J.J.

13 (= my S= ney Sum 0 carry. fight Implementation of HA Full Addes The process of addition proceeds ma bit-by-bit basis, right to left. beginning with the reast significant bit A FA is a combinational cruit that forme the arithmetic sum of three his. \* It constants of three JIB . I two opps.  $p = \frac{p}{2} \frac{1}{2} \frac{1}{2}$

TIT 1018) FA: S y PIBR =2 C X 2 6 0 0 0 D (A) 0 0 0 0 0 0 0 1 1 Ď AND. 0 0 1 0 0 (JbhA D 13 () difili 1 For sum? 1001130 D 00 11 0 0  $(\Lambda$ 0 1 0 1 0 cum= xy2+ xy2+ xy2+ Į, add Jan Maismas 140 For carry 11 10 100 0' r Carry = y2tx D 2frug 0 O 0 O

The logical deagram. for the FA implemented in sop. form showninggo. & It can also implemented with two HO I me or gate as shown ing fight Sum 8. Rohb

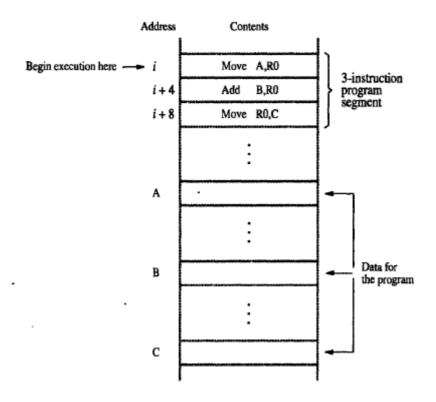

$S = \overline{z} \oplus (\mathcal{X} \oplus \mathcal{Y})$   $cont = \overline{z} (\mathcal{X} \oplus \mathcal{Y} + \overline{z} \mathcal{Y}) + \mathcal{X} \mathcal{Y}$ = 2ig2+2ig2+2ig xDy N J.O. C Brnary Adders B3 A3 Be A2 B1 A1 Bo to Cl C3 FA FA FA FA CE Cy. 53 52 S Four-bit · addes Scanned with OKEN Scanner

fig Shows. the connection of town full -adder (PA) ckt to provide a por-bit binary - ripple carry addes. B3B2B1B0 2A2ALAO. let consider eg: A=1011 B=0011 Sum=1110 isformed. 1 the child = 12 a preparties that it's Subscript: P. 3.2 10 J/plany DILLD Ci Augend Addend 0 0 1 The Oral St. sum Oldo 1 Cifi DIPCarry 1.51 de any Republication all all to get pinal value . may after to that style had bein porpet

Carry propagation in hunder \* Addition of two binary numberlin Parallel implies that all the bits of the augund gaddechd ore available for computation at the same time. + The total propagation time is equal to the delay of a typical gate; Ames the number of gates levels in the linuit. + The longest propaga kon delay time in an adder. is the time it takes the carry to propagate. through. the fall adder. & since each bit of the sum of depends on the value of the 1/p carry. + si at any stage on all adder will be to get final vælue mlyafter the Ip carry to that stage has been propagated.

19 X to get sz value, it depends on the I/P A3, B3 & C3. but we have immediate Values of A3. B3 because our 1/ps and but E C3 JIP C3 Will wait to get value untell cz isavailable. to seadde, from the previous stuge. 11 of c2. has to wait for c1. 9 so on down to co. + Thus only after the cavity propagates of sipples. through all stages . will the last 0/p-538 (y. settle to their final corretuolier. \* For this resim the cht of the cambe redrawn as HAT I'V of polis HATTER PItcy Sp Giv PSG: thi rti ( )

\* Here Ilp i tothe Olp Citi propagatel mough an AND geile I anorgate \* too gate levels. to ' 4-FA: madder. Olp (4. would have 274=8 gate levels. from Coto Cy. & The carry propagation time is an important characterristic of the ceddles because it limits the speed with which two numbers · are added. \* An obvious som for reducing the carry pdit is to employ fastor gates with reduced telays. I Another SIZ is to increasing the itet complexity to greduce carry delay. \* The most widely ised technique em is carry lookahead logic.

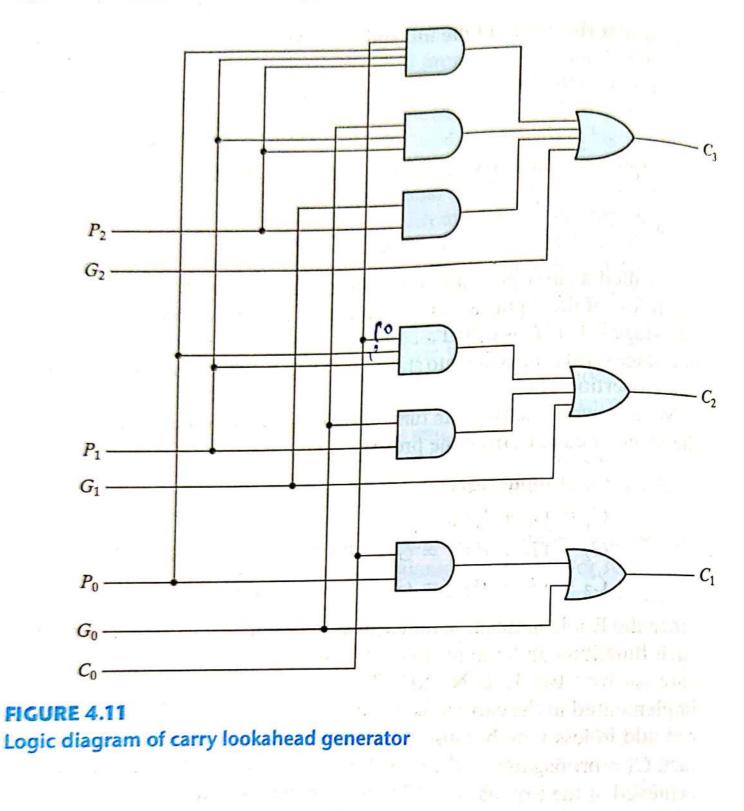

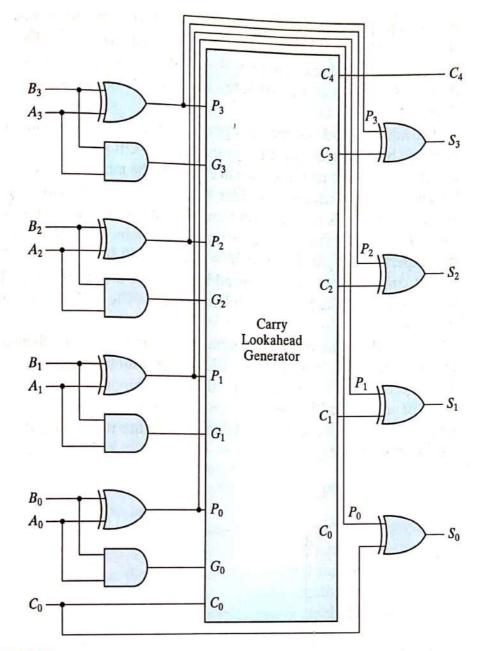

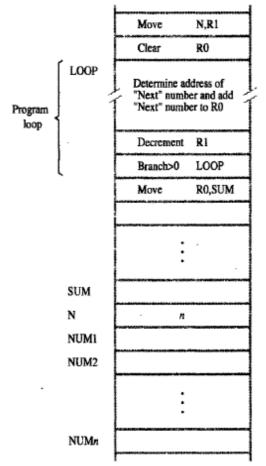

$P_i = A_i(f) B_i$ Gi = APBi. Ops vC Si= Pr@Cr CP+1= Gi+Pici Gi - camp generates pi - is called carry propagate \* let us write carry old \$ too early CD = JIP Carry Stage. CI= Got Po Co  $C_2 = G_1 + P_1 C_1 = G_1 + P_1 (G_0 + P_0 G)$ = GI+PiGo+ PiPolo  $c_3 = f_2 + P_2 (2 = f_2 + P_2 (G_1 + P_1 G_0 + P_1 P_0 G))$ = G2+P2G1+BPiGo+P2P1PoCo

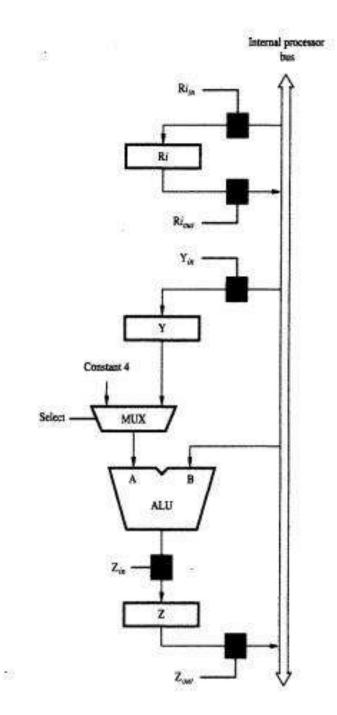

#### Binary Adder–Subtractor

**FIGURE 4.12** Four-bit adder with carry lookahead

### **Binary Subtractor**

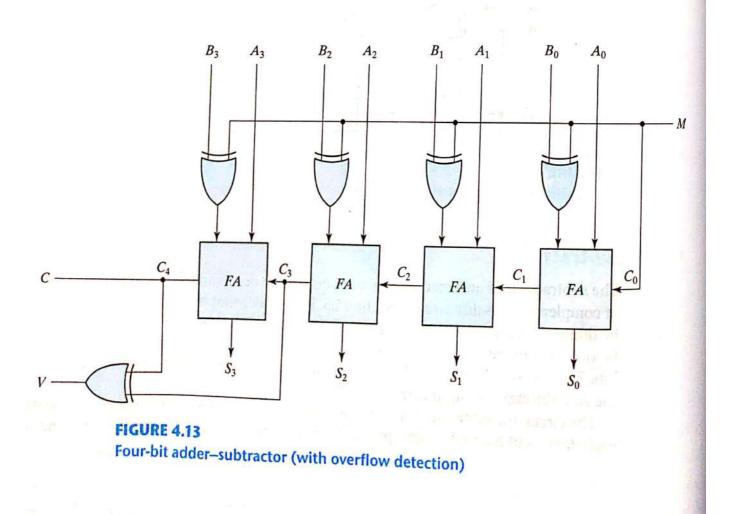

The subtraction of unsigned binary numbers can be done most conveniently by means of complements, as discussed in Section 1.5. Remember that the subtraction A - B can be done by taking the 2's complement of B and adding it to A. The 2's complement can be obtained by taking the 1's complement and adding 1 to the least significant pair of bits. The 1's complement can be implemented with inverters, and a 1 can be added to the sum through the input carry of a full adder.

The circuit for subtracting A - B consists of an adder with inverters placed between each data input B and the corresponding input of the full adder. The input carry  $C_0$  must

#### **Combinational Logic** Chapter 4 182

be equal to 1 when subtraction is performed. The operation thus performed  $be_{comes}$ be equal to 1 when subtraction is performed by a plus the 2's complement of B, plus the 1's complement of B, plus 1. This is equal to A plus the 2's complement of (B, B). A, plus the 1's complement of B, plus A miner  $A \ge B$  or the 2's complement of  $(B \ge A)$ . For unsigned numbers, that gives A - B if  $A \ge B$  or the 2's complement of  $(B \ge A)$ . if A < B. For signed numbers, the result is A - B, provided that there is no  $ov_{er}$ . flow. (See Section 1.6.)

The addition and subtraction operations can be combined into one circuit with one common binary adder by including an exclusive-OR gate with each full adder. A four-bit adder-subtractor circuit is shown in Fig. 4.13. The mode input M controls the operation. When M = 0, the circuit is an adder, and when M = 1, the circuit becomes a subtractor Each exclusive-OR gate receives input M and one of the inputs of B. When M = 0, we have  $B \oplus 0 = B$ . The full adders receive the value of B, the input carry is 0, and the circuit performs A plus B. When M = 1, we have  $B \oplus 1 = B'$  and  $C_0 = 1$ . The B inputs are all complemented and a 1 is added through the input carry. The circuit performs the operation A plus the 2's complement of B. (The exclusive-OR with output V is for detecting an overflow.)

It is worth noting that binary numbers in the signed-complement system are added and subtracted by the same basic addition and subtraction rules as are unsigned numbers. Therefore, computers need only one common hardware circuit to handle both types of arithmetic. The user or programmer must interpret the results of such addition or subtraction differently, depending on whether it is assumed that the numbers are signed or unsigned.

## Practice Exercise 4.6

Find A-B with  $A = 1001_2$  and  $B = 0110_2$ ;

**Answer:**  $A-B = 1_{0011_2}$

# overflow

When two numbers with n digits each are added and the sum is a number occupying n + 1 digits, we say that an overflow occurred. This is true for binary or decimal numbers, signed or unsigned. When the addition is performed with paper and pencil, an overflow is not a problem, since there is no limit by the width of the page to write down the sum.) Overflow is a problem in digital computers because the number of bits that hold the number is finite and a result that contains n + 1 bits cannot be accommodated by an n-bit word. For this reason, many computers detect the occurrence of an overflow, and when it occurs, a corresponding flip-flop is set that can then be checked by the user.

The detection of an overflow after the addition of two binary numbers depends on whether the numbers are considered to be signed or unsigned. When two unsigned numbers are added, an overflow is detected from the end carry out of the most significant position. In the case of signed numbers, two details are important: the leftmost bit always represents the sign, and negative numbers are in 2's-complement form. When two signed numbers are added, the sign bit is treated as part of the number and the end carry does not indicate an overflow.

An overflow cannot occur after an addition if one number is positive and the other is negative, since adding a positive number to a negative number produces a result whose magnitude is smaller than the larger of the two original numbers. An overflow may occur if the two numbers added are both positive or both negative. To see how this can happen, consider the following example: Two signed binary numbers, +70 and +80, are stored in two eight-bit registers. The range of numbers that each register can accommodate is from binary +127 to binary -128. Since the sum of the two numbers is +150, it exceeds the capacity of an eight-bit register. This is also true for -70 and -80. The two additions in binary are shown next, together with the last two carries:

| carries: | 01        | carries: | 01        |

|----------|-----------|----------|-----------|

| +70      | 0 1000110 | -70      | 1 0111010 |

| +80      | 0 1010000 | -80      | 1 0110000 |

| 150      | 1 0010110 | -150     | 0 1101010 |

Note that the eight-bit result that should have been positive has a negative sign bit (i.e., the eighth bit) and the eight-bit result that should have been negative has a positive sign bit. If, however, the carry out of the sign bit position is taken as the sign bit of the result, then the nine-bit answer so obtained will be correct. But since the answer cannot be accommodated within eight bits, we say that an overflow has occurred.

An overflow condition can be detected by observing the carry into the sign bit position and the carry out of the sign bit position. If these two carries are not equal, an overflow has occurred. This is indicated in the examples in which the two carries are explicitly shown. If the two carries are applied to an exclusive-OR gate, an overflow is detected when the output of the gate is equal to 1. For this method to work correctly, the 2's complement of a negative number must be computed by taking the 1's complement and adding 1. This takes care of the condition when the maximum negative number is complemented.

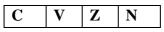

The binary adder-subtractor circuit with outputs C and V is shown in Fig. 4.13. If the two binary numbers are considered to be unsigned, then the C bit detects a carry after addition or a borrow after subtraction. If the numbers are considered to be signed, then the V bit detects an overflow. If V = 0 after an addition or subtraction, then no overflow occurred and the *n*-bit result is correct. If V = 1, then the result of the operation contains n + 1 bits, but only the rightmost *n* bits of the number fit in the space available, so an overflow has occurred. The (n + 1) th bit is the actual sign and has been shifted out of position.

#### DECODERS 4.9

Discrete quantities of information are represented in digital systems by binary codes. A binary code of n bits is capable of representing up to  $2^n$  distinct elements of coded information. A decoder is a combinational circuit that converts binary information from n input lines to a maximum of  $2^n$  unique output lines. If the *n*-bit coded information has unused combinations, the decoder may have fewer than  $2^n$  outputs.

The decoders presented here are called *n*-to-*m*-line decoders, where  $m \leq 2^n$ . Their purpose is to generate the  $2^n$  (or fewer) minterms of n input variables. Each combination of inputs will assert a unique output. The name decoder is also used in conjunction with other code converters, such as a BCD-to-seven-segment decoder.

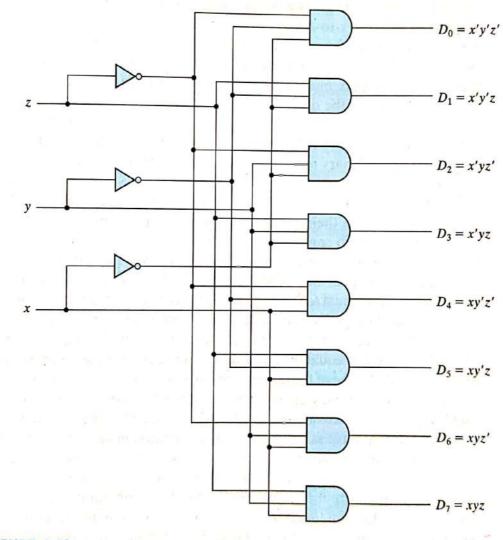

As an example, consider the three-to-eight-line decoder circuit of Fig. 4.18. The three inputs are decoded into eight outputs, each representing one of the minterms of the three input variables. The three inverters provide the complement of the inputs, and each

FIGURE 4.18 Three-to-eight-line decoder

#### Chapter 4 Combinational Logic 192

| Inputs |   | Outputs |    |                |                |                |                |                |   |

|--------|---|---------|----|----------------|----------------|----------------|----------------|----------------|---|

| x      | y | z       | Do | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D |

| 0      | 0 | 0       | 1  | 0              | 0              | 0              | 0              | 0              | 0 |

| 0      | 0 | 1       | 0  | 1              | 0              | 0              | 0              | 0              | 0 |

| 0      | 1 | 0       | 0  | 0              | 1              | 0              | 0              | 0              | 0 |

| 0      | 1 | 1       | 0  | 0              | 0              | 1              | 0              | 0              | 0 |

| 1      | 0 | 0       | 0  | 0              | 0              | 0              | 1              | 0              | 0 |

| 1      | 0 | 1       | 0  | 0              | 0              | 0              | 0              | 1              | 0 |

| 1      | 1 | 0       | 0  | 0              | 0              | 0              | 0              | 0              | 1 |

| 1      | 1 | 1       | 0  | 0              | 0              | 0              | 0              | 0              | 0 |

Table 4.6 at the time Decedar

one of the eight AND gates generates one of the minterms. A particular application of this decoder is binary-to-octal conversion. The input variables represent a binary num. ber, and the outputs represent the eight digits of a number in the octal number system. However, a three-to-eight-line decoder can be used for decoding any three-bit code to provide eight outputs, one for each element of the code.

The operation of the decoder may be clarified by the truth table listed in Table 4.6. For each possible input combination, there are seven outputs that are equal to 0 and only one that is equal to 1. The output whose value is equal to 1 represents the minterm equivalent of the binary number currently available in the input lines.

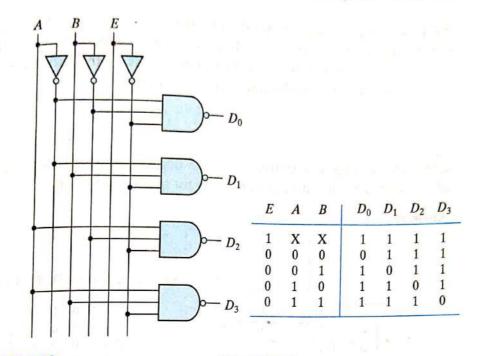

Some decoders are constructed with NAND gates. Since a NAND gate produces the AND operation with an inverted output, it becomes more economical to generate the decoder minterms in their complemented form. Furthermore, decoders include one or more enable inputs to control the circuit operation. A two-to-four-line decoder with an enable input constructed with NAND gates is shown in Fig. 4.19. The circuit operates with complemented outputs and a complement enable input. The outputs of the decoder are enabled when E is equal to 0 (i.e., active-low enable). As indicated by the truth table, only one output can be equal to 0 at any given time; all other outputs are equal to 1. The output whose value is equal to 0 represents the minterm selected by inputs A and B. The circuit is disabled when E is equal to 1, regardless of the values of the other two inputs. When the circuit is disabled, none of the outputs are equal to 0 and none of the minterms are selected. In general, a decoder may operate with complemented or uncomplemented outputs. The enable input may be activated with a 0 or with a 1 signal. Some decoders have two or more enable inputs that must satisfy a given logic condition in order to enable the circuit.

A decoder with enable input can function as a demultiplexer-a circuit that receives information from a single line and directs it to one of 2" possible output lines. The selection of a specific output is controlled by the bit combination of n selection lines. The decoder of Fig. 4.19 can function as a one-to-four-line demultiplexer when E is taken as a data input line and A and B are taken as the selection inputs. The single input variable Ehas a path to all four outputs, but the input information is directed to only one of the output lines, as specified by the binary combination of the two selection lines A and B. This

FIGURE 4.19 Two-to-four-line decoder with enable input

feature can be verified from the truth table of the circuit. For example, if the selection lines AB = 10, output  $D_2$  will be the same as the input value E, while all other outputs are maintained at 1. Because decoder and demultiplexer operations are obtained from the same circuit, a decoder with an enable input is referred to as a *decoder demultiplexer*.

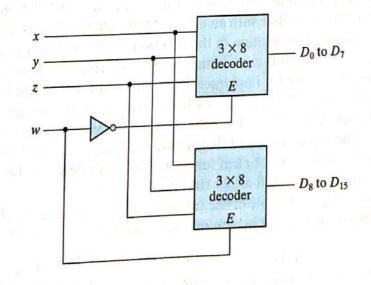

Decoders with enable inputs can be connected together to form a larger decoder circuit. Figure 4.20 shows two 3-to-8-line decoders with enable inputs connected to form a 4-to-16-line decoder. When w = 0, the top decoder is enabled and the other is disabled. The bottom decoder outputs are all 0's, and the top eight outputs generate minterms 0000 to 0111. When w = 1, the enable conditions are reversed: The bottom decoder outputs generate minterms 1000 to 1111, while the outputs of the top decoder are all

### 14 Chapter 4 Combinational Logic

0's. This example demonstrates the usefulness of enable inputs in decoders and other combinational logic components. In general, enable inputs are a convenient feature for interconnecting two or more standard components for the purpose of combining them into a similar function with more inputs and outputs.

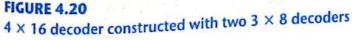

### Practice Exercise 4.8

Draw a logic diagram constructing a  $3\times8$  decoder with active-low enable, using a pair of  $2\times4$  decoders; also draw a truth table for the configuration.

### Answer:

# ombinational Logic Implementation

A decoder provides the  $2^n$  minterms of n input variables. Each asserted output of the decoder is associated with a unique pattern of input bits. Since any Boolean function can be expressed in sum-of-minterms form, a decoder that generates the minterms of the function, together with an external OR gate that forms their logical sum, provides a hardware implementation of the function. In this way, any combinational circuit with n inputs and m outputs can be implemented with an external OR gate that forms their logical sum, provides a sum of the function.

inputs and m outputs can be implemented with an n-to- $2^n$ -line decoder and m OR gates. The procedure for implementing a combinational circuit by means of a decoder and OR gates requires that the Boolean function for the circuit be expressed as a sum of minterms. A decoder is then chosen that generates all the minterms of the input variables. The inputs to each OR gate are selected from the decoder outputs according to the list of minterms of each function. This procedure will be illustrated by an example

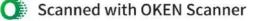

From the truth table of the full-adder (see Table 4.4), we obtain the functions for the combinational circuit in sum-of-minterms form:

$S(x, y, z) = \Sigma(1, 2, 4, 7)$  $C(x, y, z) = \Sigma(3, 5, 6, 7)$

**FIGURE 4.21** Implementation of a full adder with a decoder

Since there are three inputs and a total of eight minterms, we need a three-to-eightline decoder. The implementation is shown in Fig. 4.21. The decoder generates the eight minterms for x, y, and z. The OR gate for output S forms the logical sum of minterms 1, 2, 4, and 7. The OR gate for output C forms the logical sum of minterms 3, 5, 6, and 7.

A function with a long list of minterms requires an OR gate with a large number of inputs. A function having a list of k minterms can be expressed in its complemented form F' with  $2^n - k$  minterms. If the number of minterms in the function is greater than  $2^{n}/2$ , then F' can be expressed with fewer minterms. In such a case, it is advantageous to use a NOR gate to sum the minterms of F'. The output of the NOR gate complements this sum and generates the normal output F. If NAND gates are used for the decoder, as in Fig. 4.19, then the external gates must be NAND gates instead of OR gates. This is because a two-level NAND gate circuit implements a sum-of-minterms function and is equivalent to a two-level AND-OR circuit.

#### 4.10 ENCODERS

An encoder is a digital circuit that performs the inverse operation of a decoder. An encoder has  $2^n$  (or fewer) input lines and n output lines. The output lines, as an aggregate, generate the binary code corresponding to each input value. An example of an encoder is the octal-to-binary encoder whose truth table is given in Table 4.7. It has eight inputs (one for each of the octal digits) and three outputs that generate the corresponding binary number. It is assumed that only one input has a value of 1 at any given time.

The encoder can be implemented with OR gates whose inputs are determined directly from the truth table. Output z is equal to 1 when the input octal digit is 1, 3, 5,

#### Chapter 4 Combinational Logic 196

or 7. Output y is 1 for octal digits 2, 3, 6, or 7, and output x is 1 for digits 4, 5, 6, or 7. These conditions can be expressed by the following Boolean output functions:

$$z = D_1 + D_3 + D_5 + D_7$$

$$y = D_2 + D_3 + D_6 + D_7$$

$$x = D_4 + D_5 + D_6 + D_7$$

The encoder can be implemented with three OR gates.

The encoder defined in Table 4.7 has the limitation that only one input can be active at any given time. If two inputs are active simultaneously, the output produces an unde fined combination. For example, if  $D_3$  and  $D_6$  are 1 simultaneously, the output of the encoder will be 111 because all three outputs are equal to 1. The output 111 does not represent either binary 3 or binary 6. To resolve this ambiguity, encoder circuits must establish an input priority to ensure that only one input is encoded. If we establish a higher priority for inputs with higher subscript numbers, and if both  $D_3$  and  $D_6$  are 1 at the same time, the output will be 110 because  $D_6$  has higher priority than  $D_3$ .

Another ambiguity in the octal-to-binary encoder is that an output with all 0's is generated when all the inputs are 0; but this output is the same as when  $D_0$  is equal to 1. The discrepancy can be resolved by providing one more output to indicate whether at least one input is equal to 1.

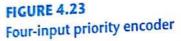

### **Priority Encoder**

A priority encoder is an encoder circuit that includes the priority function, and handles the possibility that inputs might be in contention. The operation of the priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence. The truth table of a four-input priority encoder is given in Table 4.8. In addition to the two outputs x and y, the circuit has a third output designated by V; this is a valid bit indicator that is set to 1 when one or more inputs are equal to 1. If all inputs are 0, there is no valid input, and V is equal to 0. The other two

| Inputs |                |                |                |                |    |                |    |           |           | Output | ts |

|--------|----------------|----------------|----------------|----------------|----|----------------|----|-----------|-----------|--------|----|

| Do     | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | Ds | D <sub>6</sub> | D7 | - · · ·   | x         | y      | z  |

| 1      | 0              | 0              | 0              | 0              | 0  | 0              | 0  | 784 18 1  | 0         | 0      | 0  |

| 0      | 1              | 0              | 0              | 0              | 0  | 0              | 0  |           | 0         | 0      | 1  |

| 0      | 0              | 1              | 0              | 0              | 0  | 0              | 0  |           | 0         | 1      | 0  |

| 0      | 0              | 0              | 1              | 0              | 0  | 0              | 0  |           | 0         | uni    | 1  |

| 0      | 0              | 0              | 0              | 1              | 0  | 0              | 0  | 22 2 20 3 | 1         | 0      | 0  |

| 0      | 0              | 0              | 0              | 0              | 1  | 0              | 0  |           | 19 (P 10) | 0      | 1  |

| 0      | 0              | 0              | 0              | 0              | Ô  | 1              | 0  |           | ាន🗘 ខា    |        | 0  |

| 0      | 0              | 0              | 0              | 0              | 0  | 0              | 1  |           | 110       | 1      | 1  |

### Table 4.7

Truth Table of an Octal-to-Binary Encoder

Table 4.8 Truth Table of a Priority Encoder

|    | Inp            | outs           |                | Outputs |     |   |  |

|----|----------------|----------------|----------------|---------|-----|---|--|

| Do | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | x       | y   | V |  |

| 0  | 0              | 0              | 0              | х       | x   | 0 |  |

| 1  | 0              | 0              | 0              | 0       | 0   | 1 |  |

| Х  | V              | 0              | 0              | 0       | 1   | 1 |  |

| X  | X              | 1              | 0              | 1       | 0   | 1 |  |

| X  | X              | Х              | 1              | 1       | - 1 | 1 |  |

outputs are not inspected when V equals 0, and are specified as don't-care conditions. Note that whereas X's in output columns represent don't-care conditions, the X's in the input columns are useful for representing a truth table in condensed form. Instead of listing all 16 minterms of four variables, the truth table uses an X to represent either 1 or 0. For example, X100 represents the two minterms 0100 and 1100.

According to Table 4.8, the higher the subscript number, the higher the priority of the input is. Input  $D_3$  has the highest priority, so, regardless of the values of the other inputs, when this input is 1, the output for xy is 11 (binary 3).  $D_2$  has the next priority level. The output is 10 if  $D_2 = 1$ , provided that  $D_3 = 0$ , regardless of the values of the other two lower priority inputs. The output for  $D_1$  is generated only if higher priority inputs are 0, and so on down the priority levels.

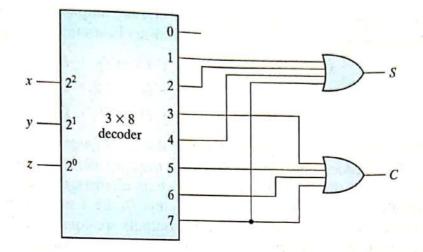

The K-maps for simplifying outputs x and y are shown in Fig. 4.22. The minterms for the two functions are derived from Table 4.8. Although the table has only five rows, when each X in a row is replaced first by 0 and then by 1, we obtain all 16 possible input combinations. For example, the fourth row in the table, with inputs XX10, represents the

198

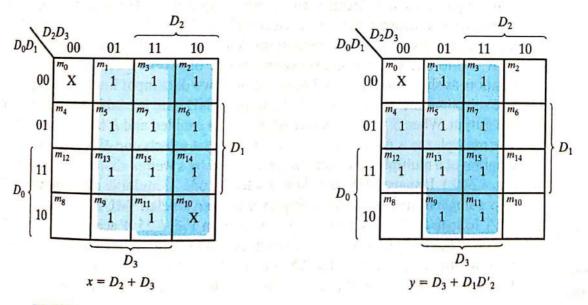

four minterms 0010, 0110, 1010, and 1110. The simplified Boolean expressions for the priority encoder are obtained from the maps. The condition for output V is an OR function of all the input variables. The priority encoder is implemented in Fig. 4.23 according to the following Boolean functions:

$$x = D_2 + D_3$$

$$y = D_3 + D_1 D'_2$$

$$V = D_0 + D_1 + D_2 + D_3$$

## .11 MULTIPLEXERS

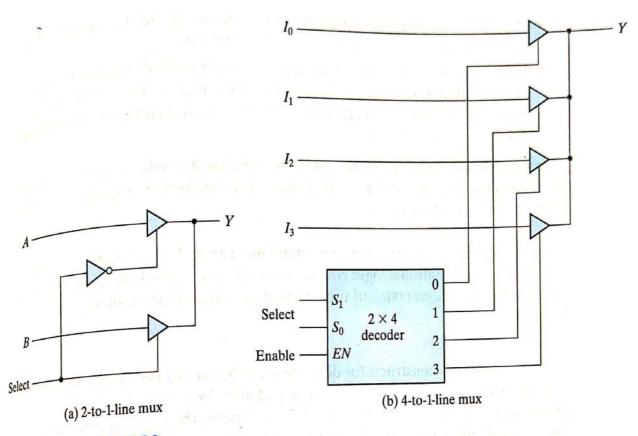

A multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line.<sup>6</sup> The selection of a particular input line is controlled by a set of selection lines. Normally, there are  $2^n$  input lines and *n* selection lines whose bit combinations determine which input is selected.

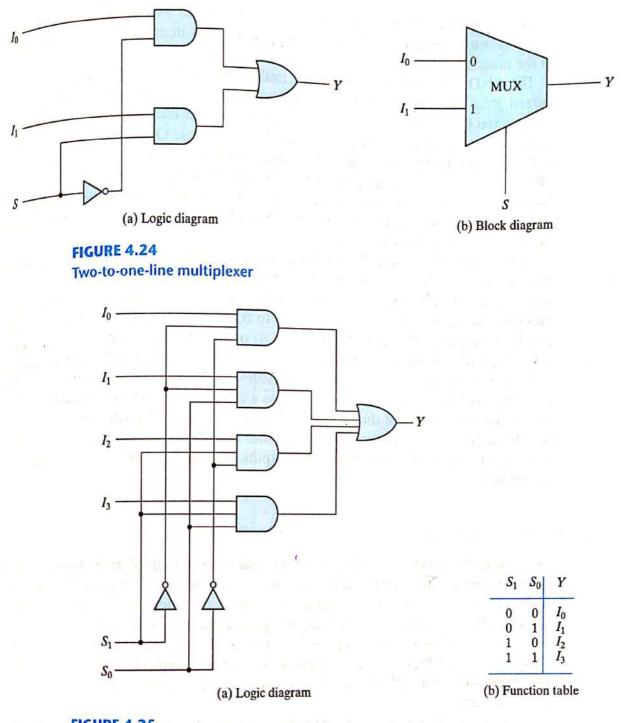

A two-to-one-line multiplexer connects one of two 1-bit sources to a common destination, as shown in Fig. 4.24. The circuit has two data input lines, one output line, and one selection line S. When S = 0, the upper AND gate is enabled and  $I_0$  has a path to the output. When S = 1, the lower AND gate is enabled and  $I_1$  has a path to the output. The multiplexer acts like an electronic switch that selects one of two sources. The block diagram of a multiplexer is sometimes depicted by a wedge-shaped symbol, as shown in Fig. 4.24(b). It suggests visually how a selected one of multiple data sources is directed into a single destination. The multiplexer is often labeled "MUX" in block diagrams.

A four-to-one-line multiplexer is shown in Fig. 4.25. Each of the four inputs,  $I_0$  through  $I_3$ , is applied to one input of an AND gate. Selection lines  $S_1$  and  $S_0$  are decoded to select a particular AND gate. The outputs of the AND gates are applied to a single OR gate that provides the one-line output. The function table lists the

<sup>&</sup>lt;sup>6</sup>Lines represent signals in circuit drawings. It is common usage to refer to input and output signals of a multiplexer as input and output lines.

FIGURE 4.25 Four-to-one-line multiplexer

input that is passed to the output for each combination of the binary selection values. To demonstrate the operation of the circuit, consider the case when  $S_1S_0 = 10$ . The AND gate associated with input  $I_2$  has two of its inputs equal to 1 and the third input connected to  $I_2$ . The other three AND gates have at least one input equal to 0, which makes their outputs equal to 0. The output of the OR gate is now equal to the value of

# **Boolean Function Implementation with Multiplexers**

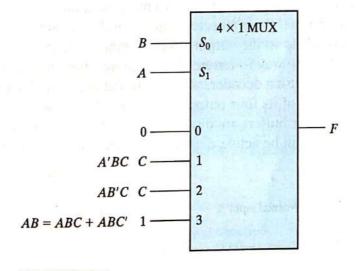

In Section 4.9, it was shown that a decoder can be used to implement Boolean functions by employing external OR gates. An examination of the logic diagram of a multiplexer reveals that it is essentially a decoder that includes the OR gate within the unit. The minterms of a function are generated in a multiplexer by the circuit associated with the selection inputs. The individual minterms can be selected by the data inputs, thereby providing a method of implementing a Boolean function of nvariables with a multiplexer that has n selection inputs and  $2^n$  data inputs, one for each minterm.

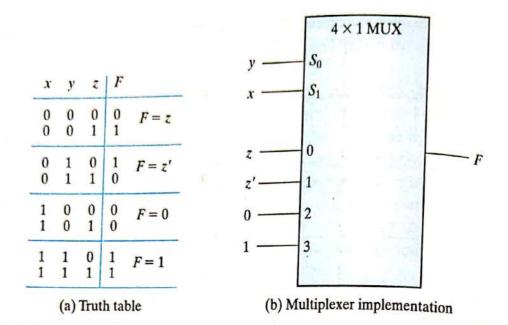

We will now show a more efficient method for implementing a Boolean function of n variables with a multiplexer that has n - 1 selection inputs, instead of n selection inputs. The first n - 1 variables of the function are connected to the selection inputs of the multiplexer. The remaining single variable of the function is used for the data inputs. If the single variable is denoted by z, each data input of the multiplexer will be z, z', 1, or 0. To demonstrate this procedure, consider the Boolean function

$F(x, y, z) = \Sigma(1, 2, 6, 7)$

### **FIGURE 4.27**

Implementing a Boolean function with a multiplexer

xy = 00, data input 0 has a path to the output, and that makes F equal to z. In a similar fashion, we can determine the required input to data lines 1, 2, and 3 from the value of F when xy = 01, 10, and 11, respectively. This particular example shows all four possibilities that can be obtained for the data inputs.

The general procedure for implementing any Boolean function of n variables with a multiplexer with n - 1 selection inputs and  $2^{n-1}$  data inputs follows from the previous example. To begin with, Boolean function is listed in a truth table. Then first n - 1variables in the table are applied to the selection inputs of the multiplexer. For each combination of the selection variables, we evaluate the output as a function of the last variable. This function can be 0, 1, the variable, or the complement of the variable. These values are then applied to the data inputs in the proper order.

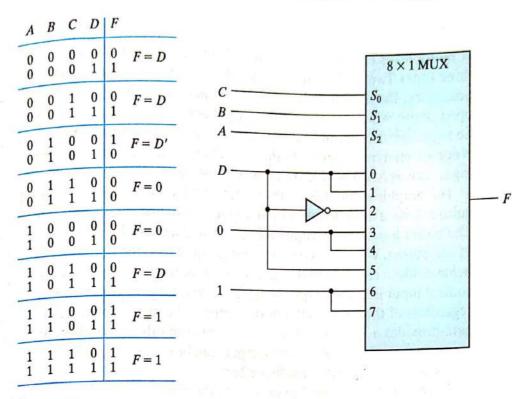

As a second example, consider the implementation of the Boolean function

$$F(A, B, C, D) = \Sigma(1, 3, 4, 11, 12, 13, 14, 15)$$

This function is implemented with a multiplexer with three selection inputs as shown in Fig. 4.28. Note that the first variable A must be connected to selection input  $S_2$  so that A, B, and C correspond to selection inputs  $S_2$ ,  $S_1$ , and  $S_0$ , respectively. The values for the data inputs are determined from the truth table listed in the figure. The corresponding data line number is determined from the binary combination of ABC. For example, the table shows that when ABC = 101, F = D, so the input variable D is applied to data input 5. The binary constants 0 and 1 correspond to two fixed signal values. When integrated circuits are used, logic 0 corresponds to signal ground and logic 1 is equivalent to the power signal, depending on the technology (e.g., 3 V).

### FIGURE 4.28 Implementing a four-input function with a multiplexer

## Practice Exercise 4.9

Implement the Boolean function  $F(A, B, C) = \Sigma(3, 5, 6, 7)$  with a multiplexer.

Answer:

1

### **FIGURE PE4.9**

#### **Three-State Gates**

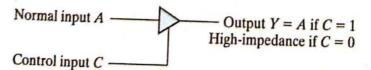

A multiplexer can be constructed with three-state gates-digital circuits that exhibit A multiplexer can be constructed with under the logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a <math>conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and logic 0 as in a conventthree states. Two of the states are signals equivalent to logic 1 and lthree states. Two of the states are signate equation which (1) the logic behaves like an tional gate. The third state is a high-impedance state in which (1) the logic behaves like an tional gate. The third state is a *high unpetitive* appears to be disconnected, (2) the circuit  $h_{as}$  open circuit, which means that the output appears to the output of the three states  $h_{as}$ no logic significance, and (3) the circuit connected to the output of the three-state gate is not affected by the inputs to the gate. Three-state gates may perform any conventional logic, such as AND or NAND. However, the one most commonly used is the buffer gate.

The graphic symbol for a three-state buffer gate is shown in Fig. 4.29. It is distinguished from a normal buffer by an input control line entering the bottom of the symbol. The buffer has a normal input, an output, and a control input that determines the state of the output. When the control input is equal to 1, the output is enabled and the gate behaves like a conventional buffer, with the output equal to the normal input. When the control input is 0, the output is disabled and the gate goes to a high-impedance state, regardless of the value in the normal input. The high-impedance state of a three-state gate provides a special feature not available in other gates. Because of this feature, a large number of three-state gate outputs can be connected with wires to form a common line without endangering loading effects.

The construction of multiplexers with three-state buffers is demonstrated in Fig. 4.30. Figure 4.30(a) shows the construction of a two-to-one-line multiplexer with 2 threestate buffers and an inverter. The two outputs are connected together to form a single output line. (Note that this type of connection cannot be made with gates that do not have three-state outputs.) When the selected input is 0, the upper buffer is enabled by its control input and the lower buffer is disabled. Output Y is then equal to input A. When the select input is 1, the lower buffer is enabled and Y is equal to B.

The construction of a four-to-one-line multiplexer is shown in Fig. 4.30(b). The outputs of 4 three-state buffers are connected together to form a single output line. The control inputs to the buffers determine which one of the four normal inputs  $I_0$  through  $I_3$  will be connected to the output line. No more than one buffer may be in the active state at any given time. The connected buffers must be controlled so that only 1 threestate buffer has access to the output while all other buffers are maintained in a highimpedance state. One way to ensure that no more than one control input is active at any given time is to use a decoder, as shown in the diagram. When the enable input of the decoder is 0, all of its four outputs are 0 and the bus line is in a high-impedance state because all four buffers are disabled. When the enable input is active, one of the three-state buffers will be active, depending on the binary value in the select inputs of

FIGURE 4.29 Graphic symbol for a three-state buffer

#### FIGURE 4.30 Multiplexers with three-state gates

the decoder. Careful investigation reveals that this circuit is another way of constructing a four-to-one-line multiplexer.

# 4.12 HDL MODELS OF COMBINATIONAL CIRCUITS

Basic features of Verilog and VHDL were introduced in Chapter 3. This section introduces additional features of those languages, presents more elaborate examples, and

compares alternative descriptions of combinational circuits.' Verilog and VHDL support three common styles of modeling combinational circuits:

• Gate-level modeling, also called *structural* modeling, instantiates and interconnects basic logic circuits to form a more complex circuit having a desired functionality. Gate-level modeling describes a circuit by specifying its gates and how they are connected with each other.<sup>8</sup>

<sup>&</sup>lt;sup>7</sup>Sequential circuits and their models are presented in Chapter 5.

<sup>8</sup>Verilog also supports switch-level modeling for directly representing MOS transistor circuits. This style is sometimes used in modeling and simulation, but not in synthesis. We will not use switch-level modeling in this text, but we provide a brief introduction in Appendix A.3. For additional information see the Verilog language reference manual.

# Table 4.10 Some Verilog Operators

| Symbol      | Operation                                            | Symbol                   | Operation                   |

|-------------|------------------------------------------------------|--------------------------|-----------------------------|

| +<br>-<br>& | binary addition<br>binary subtraction<br>bitwise AND | &&                       | logical AND                 |

| 1           | bitwise OR<br>bitwise XOR                            | L .<br>L . L Mr D. T. J. | logical OR                  |

| ~           | bitwise NOT                                          |                          | logical NOT                 |

| >           | equality greater than                                |                          |                             |

| < { }       | less than concatenation                              |                          |                             |

| ?:          | conditional                                          | 1. N. 198 - 1            | and inference of the second |

# HDL Example 4.4 (Dataflow: Two-to-Four Line Decoder)

# Verilog

// Dataflow description of two-to-four-line decoder

// See Fig. 4.19. Note: The figure uses symbol E, but the

// Verilog model uses enable to clearly indicate functionality.

module decoder\_2x4\_df ( // Verilog 2001, 2005 syntax output [0: 3] D, input A, B, enable

```

);

assign D[0] = !((!A) && (!B) && (!enable)),

D[1] = !((!A) && B && (!enable)),

D[2] = ((A) && (! B) && (!enable)),

D[3] = !(A && B && (!enable));

endmodule

```

# HDL Example 4.5 (Dataflow: Four-Bit Adder)

# Verilog

```

// Dataflow description of four-bit adder

// Verilog 2001, 2005 module port syntax

module binary_adder (

output C_out,

output [3: 0] Sum,

input [3: 0] A, B,

input C_in

);

assign {C_out, Sum} = A + B + C_in // Continuous assignment statement

endmodule

```

# HDL Example 4.7 (Dataflow: Two-to-One Multiplexer)

Verilog

// Dataflow description of two-to-one-line multiplexer

module mux\_2x1\_df (m\_out, A, B, select);

output m\_out; input A, B;

input select; assign m\_out = (select)? A : B; // Conditional operator endmodule

<sup>22</sup>The conditional operator is a ternary operator, requiring three operands.

# HDL Example 4.8 (Behavioral: Alternative Two-to-Four Line Decoder)

Verilog

```

module decoder_2x4_df_beh ( // Verilog 2001, 2005 syntax

output [0: 3] D,

input

A. B.

enable

);

always @ (A, B, enable) begin

D[0] <= !((!A) && (!B) && (!enable)),

D[1] <= !((!A) && B && (!enable)),

D[2] <= !(A && (!B) && (!enable)),

D[3] <= !(A && B && (!enable));

end;

endmodule

```

# HDL Example 4.9 (Behavioral: Two-to-One Line Multiplexer)

# Verilog (Procedural Statement)

// Behavioral description of two-to-one-line multiplexer module mux\_2x1\_beh (m\_out, A, B, select);

| output | m_out;        | THE LAND OF BUILDING STREAMS STOLEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| input  | A, B, select; | in the state of the second of the second of the second sec |

| reg    | m_out;        | A STATISTICS AND A STAT |

```

always @ (A or B or select) // Alternative: always @ (A, B, select)

if (select == 1) m_out = A;

else m_out = B;

endmodule

```

# Verilog

```

// Behavioral description of four-to-one line multiplexer

// Verilog 2001, 2005 port syntax

module mux_4x1_beh

(output reg m_out,

input in_0, in_1, in_2, in_3,

input [1:0] select

);

// Verilog 2001, 2005, SV syntax

always @ (in_0, in_1, in_2, in_3, select)

case (select)

2'b00: m_out <= in_0;

2'b01: m_out <= in_1;

2'b10: m_out <= in_2;

2'b11: m_out <= in_3;

endcase

endmodule

```

#### Synchronous Sequential Logic

#### 5.1 INTRODUCTION

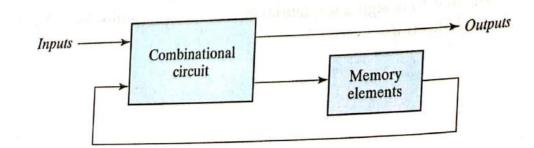

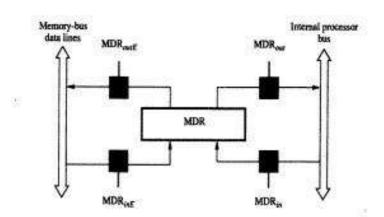

Hand-held devices, cell phones, navigation receivers, personal computers, digital can eras, personal media players, and virtually all electronic consumer products have the ability to send, receive, store, retrieve, and process information represented in a binary format. The technology enabling and supporting these devices is critically dependent on electronic components that can store information, that is, have memory. This chapter examines the operation and control of these devices and their use in circuits and enables you to better understand what is happening in these devices when you interact with them. The digital circuits considered thus far have been combinational – their output depends only and immediately on their inputs – they have no memory, that is, they do not depend on past values of their inputs. Sequential circuits, however, act as storage elements and have memory. They can store, retain, and then retrieve information when needed at a later time. It is important that you understand the distinction between sequential and combinational circuits.

#### SEQUENTIAL CIRCUITS 5.2

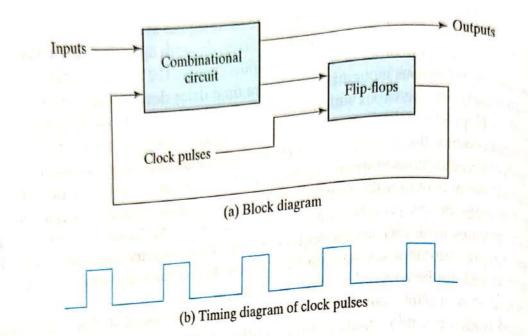

Figure 5.1 shows a block diagram of a sequential circuit. It consists of a combinational circuit to which memory elements are connected to form a feedback path. The storage elements are devices capable of storing binary information. The binary information stored in these elements at any given time defines the state of the sequential circuit at that time. The sequential circuit receives binary information from external inputs that, together with the present state of the storage elements, determine the binary value of the outputs. These external inputs also determine the condition for changing the state in the storage elements. The block diagram demonstrates that the outputs in a sequential circuit are a function not only of the inputs but also of the present state of the storage elements. The next state of the storage elements is also a function of external inputs and the present state. Thus, a sequential circuit is specified by a time sequence of inputs, outputs, and internal states. In contrast, the outputs of combinational logic depend on

There are two main types of sequential circuits, and their classification is a function of only the present values of the inputs. the timing of their signals. A synchronous sequential circuit is a system whose behavior

FIGURE 5.1 Block diagram of sequential circuit

#### Section 5.2 Sequential Circuits 263

can be defined from the knowledge of its signals at discrete instants of time. The behavjor of an asynchronous sequential circuit depends upon the input signals at any instant of time and the order in which the inputs change. The storage elements commonly used in asynchronous sequential circuits are time-delay devices. The storage capability of a timeasynche device varies with the time it takes for the signal to propagate through the device. In practice, the internal propagation delay of logic gates is of sufficient duration to produce the needed delay, so that actual delay units may not be necessary. In gate-type asynchronous systems, the storage elements consist of logic gates whose propagation delay provides the required storage. Thus, an asynchronous sequential circuit may be regarded as a combinational circuit with feedback. Because of the feedback among logic regarded as an asynchronous sequential circuit may become unstable at times. The instability gates, an imposes many difficulties on the designer, and limits their use. These circuits will not be covered in this text.

A synchronous sequential circuit employs signals that affect the storage elements at only discrete instants of time. Synchronization is achieved by a timing device called a clock generator, which provides a clock signal having the form of a periodic sequence of clock pulses. The clock signal is commonly denoted by the identifiers clock and clk. The clock pulses are distributed throughout the system in such a way that storage elements are affected only with the arrival of each pulse. In practice, the clock pulses determine when computational activity will occur within the circuit, and other signals (external inputs and otherwise) determine what changes will take place affecting the storage elements and the outputs. For example, a circuit that is to add and store two binary numbers would compute their sum from the values of the numbers and store the sum at the occurrence of a clock pulse. Synchronous sequential circuits that use clock pulses to control storage elements are called *clocked sequential circuits* and are the most frequently encountered type in practice. They are called synchronous circuits because the activity within the circuit and the resulting updating of stored values is synchronized to the occurrence of clock pulses. The design of synchronous circuits is feasible because they seldom manifest instability problems, and their timing is easily broken down into independent discrete steps, each of which can be considered separately.

The storage elements (memory) used in clocked sequential circuits are called flipflops. A flip-flop is a binary storage device capable of storing one bit of information. In a stable state, the output of a flip-flop is either 0 or 1. A sequential circuit may use many flip-flops to store as many bits as necessary. For example, a word of data may be stored as a 64-bit value. The block diagram of a synchronous clocked sequential circuit is shown in Fig. 5.2. The outputs are formed by a combinational logic function of the inputs to the circuit or the values stored in the flip-flops (or both). The value that is stored in a flip-flop when the clock pulse occurs is also determined by the inputs to the circuit or the values presently stored in the flip-flop (or both). The new value is stored (i.e., the flip-flop is updated) when a pulse of the clock signal occurs. Prior to the occurrence of the clock pulse, the combinational logic forming the next value of the flip-flop must have reached a stable value. Consequently, the speed at which the combinational logic circuits operate is critical. If the clock (synchronizing) pulses arrive at a regular interval, as shown in the timing diagram in Fig. 5.2, the combinational logic must respond to a change in

#### FIGURE 5.2 Synchronous clocked sequential circuit

the state of the flip-flop in time to be updated before the next pulse arrives. Propaga. the state of the hip-hop in time to be a minimum interval between clock tion delays play an important role in determining the minimum interval between clock pulses that will allow the circuit to operate correctly. A change in state of the flip-flops pulses that will allow the check to pulse transition - for example, when the value of the clock is initiated only by a clock pulse transition - for example, when the foodback is signals changes from 0 to 1. When a clock pulse is not active, the feedback loop between the value stored in the flip-flop and the value formed at the input to the flip-flop is effectively broken because the flip-flop outputs cannot change even if the outputs of the combinational circuit driving their inputs change. Thus, the transition from one state to the next occurs only at predetermined intervals dictated by the clock pulses.

#### Practice Exercise 5.1

Describe the fundamental difference between the output of a combinational circuit and the output of a sequential circuit.

Answer: The output of a combinational circuit depends on only the inputs to the circuit; the output of a sequential circuit depends on the inputs to the circuit and the present state of the storage elements.

#### **STORAGE ELEMENTS: LATCHES** 5.3

A storage element in a digital circuit can maintain a binary state indefinitely (as long as power is delivered to the circuit), until directed by an input signal to switch states. The major differences among various types of storage elements are in the number of inputs they possess and in the manner in which the inputs affect the binary state. Storage elements that operate with signal levels (rather than signal transitions) are referred

#### Section 5.3 Storage Elements: Latches 265

to as latches; those controlled by a clock transition are flip-flops. Latches are said to be level-sensitive devices; flip-flops are edge-sensitive devices. The two types of storage elements are related because latches are the basic circuits from which all flip-flops are constructed. Although latches are useful for storing binary information and for the design of asynchronous sequential circuits, they are not practical for use as storage elements in synchronous sequential circuits. Because they are the building blocks of flip-flops, however, we will now consider the fundamental storage mechanism used in latches before considering flip-flops in the next section.

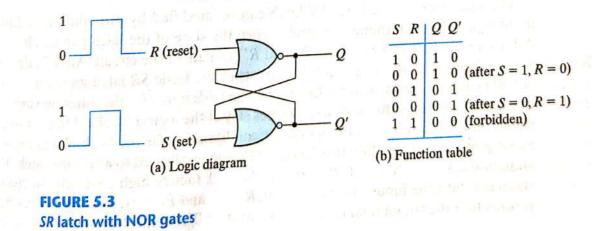

# SR Latch

The SR latch is a circuit with two cross-coupled NOR gates or two cross-coupled NAND gates, and two inputs labeled S for set, and R for reset. The SR latch constructed with two cross-coupled NOR gates is shown in Fig. 5.3. The latch has two useful states. When output Q = 1 and Q' = 0, the latch is said to be in the set state. When Q = 0 and Q' = 1, it is in the reset state. Outputs Q and Q' are normally the complement of each other. However, when both inputs are equal to 1 at the same time, a condition in which both outputs are equal to 0 (rather than be mutually complementary) occurs. If both inputs are then switched to 0 simultaneously, the device will enter an unpredictable or undefined state, called a metastable state. Consequently, in practical applications, setting both inputs to 1 is forbidden.

Under normal conditions, both inputs of the latch remain at 0 unless the state has to be changed. The application of a momentary 1 to (only) the S input causes the latch to go to the set state. The S input must go back to 0 before any other changes take place, in order to avoid the occurrence of an undefined next state that results from the forbidden input condition. As shown in the function table of Fig. 5.3(b), two input conditions cause the circuit to be in the set state. The first condition (S = 1, R = 0) is the action that must be taken by input S to bring the circuit to the set state. Removing the active input from S leaves the circuit in the same state. After both inputs return to 0, it is then possible to shift to the reset state by momentarily applying a 1 to the R input. The 1 can then be removed from R, whereupon the circuit remains in the reset state. Thus, when both inputs S and R are equal to 0, the latch can be in either the set or the reset

FIGURE 5.4 SR latch with NAND gates

state, depending on which input was most recently a 1. When inputs are applied, the resulting (next) state of the latch depends on the inputs and on the present state of the latch.

If a 1 is applied to both the S and R inputs of the latch, both outputs go to 0. This action produces an undefined next state, because the state that results from the input transitions depends on the order in which they return to 0. It also violates the requirement that outputs be the complement of each other. In normal operation, this condition is avoided by making sure that 1's are not applied to both inputs simultaneously.

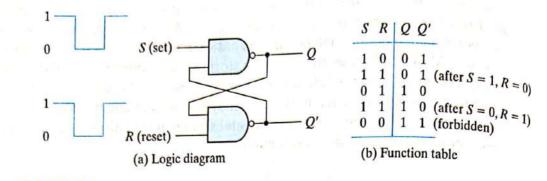

The SR latch with two cross-coupled NAND gates is shown in Fig. 5.4. It operates with both inputs normally at 1, unless the state of the latch has to be changed. The application of 0 to the S input causes output Q to go to 1, putting the latch in the set state. When the S input goes back to 1, the circuit remains in the set state. After both inputs go back to 1, we are allowed to change the state of the latch by placing a 0 in the R input. This action causes the circuit to go to the reset state and stay there even after both inputs return to 1. The condition that is forbidden for the NAND latch is both inputs being equal to 0 at the same time, an input combination that should be avoided.

In comparing the NAND with the NOR latch, note that the input signals for the NAND require the complement of those values used for the NOR latch. Because the NAND latch requires a 0 signal to change its state, it is sometimes referred to as an S'R'latch. The primes (or, sometimes, bars over the letters) designate the fact that the inputs must be in their complement form to activate the circuit.

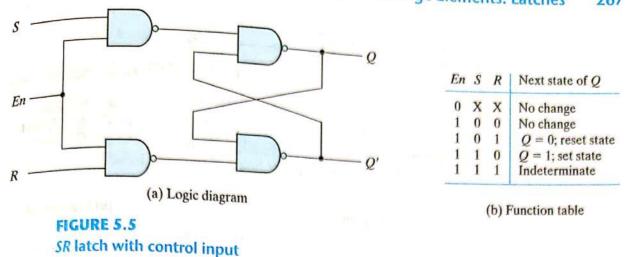

The operation of the basic SR latch can be modified by providing an additional input signal that determines (controls) when the state of the latch can be changed by determining whether S and R (or S' and R') can affect the circuit. An SR latch with a control input is shown in Fig. 5.5. It consists of the basic SR latch and two additional NAND gates. The control input En acts as an enable signal for the other two inputs. The outputs of the two additional NAND gates stay at the logic-1 level as long as the enable signal remains at 0. This is the quiescent condition for the SR latch. When the enable input goes to 1, information from the S or R input is allowed to affect the latch. The set state is reached with S = 1, R = 0, and En = 1 (active-high enabled). To change to the reset state, the inputs must be S = 0, R = 1, and En = 1. In either case, when En returns to 0, the circuit remains in its current state. The control input disables the circuit

#### Section 5.3 Storage Elements: Latches 267

by applying 0 to En, so that the state of the output does not change regardless of the values of S and R. Moreover, when En = 1 and both the S and R inputs are equal to 0, the state of the circuit does not change. These conditions are listed in the function table accompanying the diagram.

An indeterminate condition occurs when all three inputs are equal to 1. This condition places 0's on both inputs of the basic SR latch, which puts it in the undefined state. When the enable input goes back to 0, one cannot conclusively determine the next state, because it depends on whether the S or R input goes to 0 first. This indeterminate condition makes this circuit difficult to manage, and it is seldom used in practice. Nevertheless, the SR latch is an important circuit because other useful latches and flip-flops are constructed from it.

#### Practice Exercise 5.2

(a) What input condition puts an SR NOR latch into an indeterminate state?

Answer: Both inputs are 1.

(b) What input condition puts an SR NAND latch into an indeterminate state?

Answer: Both inputs are 0.

#### D Latch (Transparent Latch)

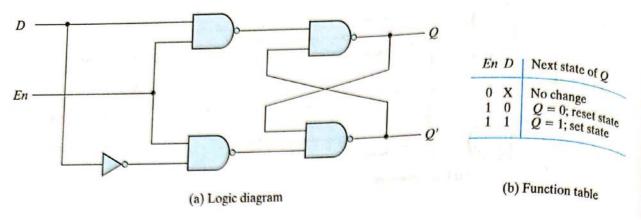

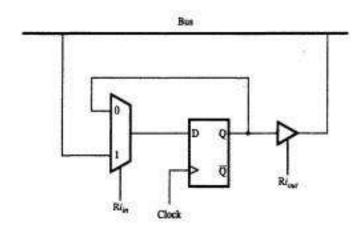

One way to eliminate the undesirable condition of the indeterminate state in the SRlatch is to ensure that inputs S and R are never equal to 1 at the same time. This is done in the D latch, shown in Fig. 5.6. This latch has only two inputs: D (data) and En (enable). The D input goes directly to the S input, and its complement is applied to the R input. As long as the enable input is at 0, the cross-coupled SR latch has both inputs at the 1 level and the circuit cannot change state regardless of the value of D. The D input is sampled when En = 1. If D = 1, the Q output goes to 1, placing the circuit in the set state. If D = 0, output Q goes to 0, placing the circuit in the reset state.

### 268 Chapter 5 Synchronous Sequential Logic

FIGURE 5.6 D latch

The D latch receives that designation from its ability to hold data in its internal storage. It is suited for use as a temporary storage for binary information between a unit and its environment. The binary information present at the data input of the D latch is transferred to the Q output when the enable input is asserted. The output follows changes in the data input as long as the enable input is asserted. This situation provides a path from input D to the output, and for this reason, the circuit is often called a transparent latch. When the enable input signal is de-asserted, the binary information that was present at the data input at the time the transition of enable occurred is retained (i.e., stored) at the Q output until the enable input is asserted again. Note that an inverter could be placed at the enable input. Then, depending on the physical circuit, the external enabling signal will be a value of 0 (active low) or 1 (active high).

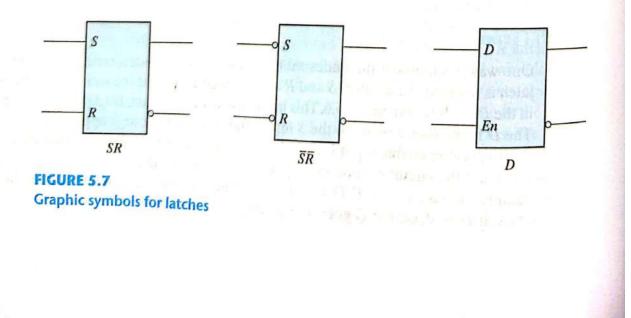

The graphic symbols for the various latches are shown in Fig. 5.7.A latch is designated by a rectangular block with inputs on the left and outputs on the right. One output designates the normal output, and the other (with the bubble designation) designates the complement output. The graphic symbol for the SR latch has inputs S and R indicated inside the block. In the case of a NAND gate latch, bubbles are added to the inputs to indicate that setting and resetting occur with a logic-0 signal. The graphic symbol for the D latch has inputs D and En indicated inside the block.

#### Practice Exercise 5.3

Describe the functionality of a transparent latch.

Answer: A transparent latch has a data input, an enable input, and output. When the enable input is asserted, the output of the latch follows the input to the latch. When the enable input is de-asserted, the output of the latch is held at the value that was present at the moment the enable input was de-asserted.

#### **STORAGE ELEMENTS: FLIP-FLOPS** 5.4

A change in the control input of a latch or flip-flop switches its state. This momentary change is called a trigger, and the transition it causes is said to trigger the flip-flop. The D latch with pulses in its control input is essentially a flip-flop that is triggered every time the pulse goes to the logic-1 level. As long as the pulse input remains at this level, any changes in the data input will change the output and the state of the latch.

As seen from the block diagram of Fig. 5.2, a sequential circuit has a feedback path from the outputs of the flip-flops to the input of the combinational circuit. Consequently, the inputs of the flip-flops are derived in part from the outputs of the same and other flip-flops. When latches are used for the storage elements, a serious difficulty arises. The state transitions of the latches start as soon as the clock pulse changes to the logic-1 level. The new state of a latch appears at the output while the pulse is still active. This output is connected to the inputs of the latches through the combinational circuit. If the inputs applied to the latches change while the clock pulse is still at the logic-1 level, the latches will respond to new values and a new output state may occur. The result is an unpredictable situation, since the state of the latches may keep changing for as long as the clock pulse stays at the active level. Because of this unreliable operation, the output of a latch cannot be applied directly or through combinational logic to the input of the same or another latch when all the latches are triggered by a common clock source.

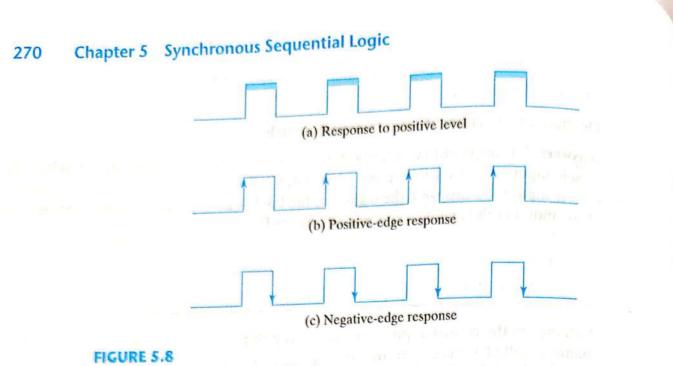

Flip-flop circuits are constructed in such a way as to make them operate properly when they are part of a sequential circuit that employs a common clock. The problem with the latch is that it responds to a change in the level of a clock pulse. As shown in Fig. 5.8(a), a positive level response in the enable input allows changes in the output when the D input changes while the clock pulse stays at logic 1. The key to the proper operation of a flip-flop is to trigger it only during a signal transition. This can be accomplished by eliminating the feedback path that is inherent in the operation of the sequential circuit using latches. A clock pulse goes through two transitions: from 0 to 1 and the return from 1 to 0. As shown in Fig. 5.8, the positive transition is defined as the positive edge and the negative transition as the negative edge. There are two ways that a latch can be modified to form a flip-flop. One way is to employ two latches in a special configuration that isolates the output of the flip-flop and prevents it from being affected while the input to the flip-flop is changing. Another way is to produce a flip-flop that triggers only during a signal transition (from 0 to 1 or from 1 to 0) of the synchronizing

#### Clock response in latch and flip-flop

signal (clock) and is disabled during the rest of the clock pulse. We will now proceed  $t_0$  show the implementation of both types of flip-flops.

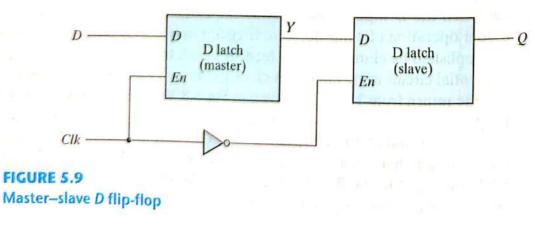

#### Edge-Triggered D Flip-Flop

The construction of a D flip-flop with two D latches and an inverter is shown in Fig. 5.9. It is often referred to as a master-slave flip-flop. The first latch is called the *master* and the second the *slave*. The circuit samples the D input and changes its output Q only at the negative edge of the synchronizing or controlling clock (designated as Clk). When Clk is 0, the output of the inverter is 1. The slave latch is enabled, and its output Q is equal to the master output Y. The master latch is disabled because Clk = 0. When the input (Clk) pulse changes to the logic-1 level, the data from the external D input are transferred to the master. The slave, however, is disabled as long as the clock remains at the 1 level, because its *enable* input is equal to 0. Any change in the input changes the master output at Y, but cannot affect the slave output. When the clock pulse returns to 0, the master is disabled and is isolated from the D input. At the same time, the slave is enabled and the value of Y is transferred to the output of the flip-flop can be triggered only by and during the transition of the clock from 1 to 0.

The behavior of the master-slave flip-flop just described dictates that (1) the output may change only once, (2) a change in the output is triggered by the negative edge of the clock, and (3) the change may occur only during the clock's negative level. The value that is produced at the output of the flip-flop is the value that was stored in the master stage immediately before the negative edge occurred. It is also possible to design the circuit so that the flip-flop output changes on the positive edge of the clock. This happens in a flip-flop that has an additional inverter between the Clk terminal and the junction between the other inverter and input En of the master latch. Such a flip-flop is triggered with a negative pulse, so that the negative edge of the clock affects the master and the positive edge affects the slave and the output terminal.

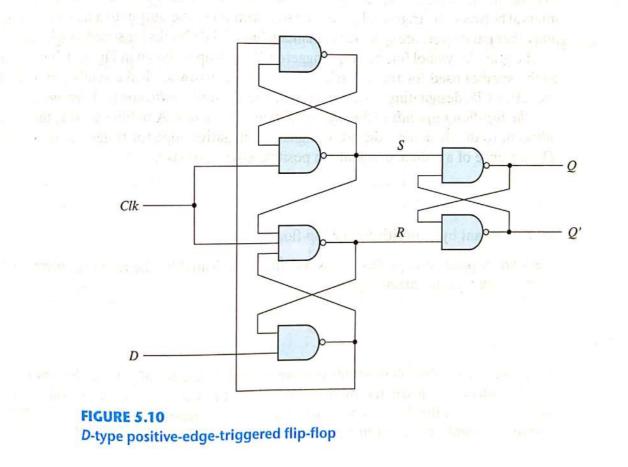

Another construction of an edge-triggered D flip-flop uses three SR latches as shown in Fig. 5.10. Two latches respond to the external D (data) and Clk (clock) inputs. The third latch provides the outputs for the flip-flop. The S and R inputs of the output latch are maintained at the logic-1 level when Clk = 0. This causes the output to remain in its present state. Input D may be equal to 0 or 1. If D = 0 when Clk becomes 1, R changes to 0. This causes the flip-flop to go to the reset state, making Q = 0. If there is a change in the D input while Clk = 1, terminal R remains at 0 because Q is 0. Thus, the flip-flop is locked out and is unresponsive to further changes in the input. When the clock returns to 0, R goes to 1, placing the output latch in the quiescent condition without changing the output. Similarly, if D = 1 when Clk goes from 0 to 1, S changes to 0. This causes the circuit to go to the set state, making Q = 1. Any change in D while Clk = 1 does not affect the output.

In sum, when the input clock in the positive-edge-triggered flip-flop makes a positive In sum, when the input clock in the positive transition of the clock (i.e., from transition, the value of D is transferred to Q. A negative transition of the clock (i.e., from transition, the value of D is transferred to Q. r in out affected by changes in D when Clk 1 to 0) does not affect the output, nor is the output Hence, this type of flip-flop respectively. 1 to 0) does not affect the output, not is the vel. Hence, this type of flip-flop responds to is in the steady logic-1 level or the logic-0 level. Hence, this type of flip-flop responds to the transition from 0 to 1 and nothing else.

The timing of the response of a flip-flop to input data and to the clock must be taken into consideration when one is using edge-triggered flip-flops. There is a minimum time called the setup time during which the D input must be maintained at a constant value prior to the occurrence of the clock transition. Similarly, there is a minimum time called the hold time during which the D input must not change after the application of the positive transition of the clock. The propagation delay time of the flip-flop is defined as the interval between the trigger edge and the stabilization of the output to a new state. These and other parameters are specified in manufacturers' data books for specific logic families.

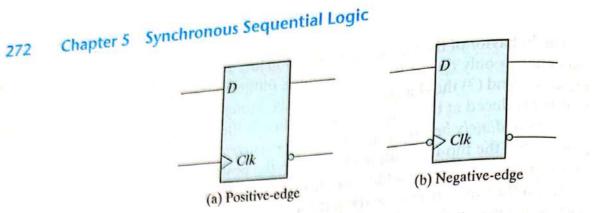

The graphic symbol for the edge-triggered D flip-flop is shown in Fig. 5.11. It is similar to the symbol used for the D latch, except for the arrowhead-like symbol in front of the letter Clk, designating a dynamic input. The dynamic indicator (>) denotes the fact that the flip-flop responds to the edge transition of the clock. A bubble outside the block adjacent to the dynamic indicator designates a negative edge for triggering the circuit. The absence of a bubble designates a positive-edge response.

#### Practice Exercise 5.4

What is meant by "a positive-edge flip-flop?"

Answer: A positive-edge flip-flop is one that is activated by the rising (positive) edge of the clock (synchronizing signal).

# **Other Flip-Flops**

Very large-scale integrated circuits contain several thousands of gates within one package. Circuits are constructed by interconnecting the various gates to provide a digi-tal system. Each flip-flop is constructed of tal system. Each flip-flop is constructed from an interconnection of gates. The most economical and efficient flip-flop constructed in this manner is the edge-triggered

D flip-flop, because it requires the smallest number of gates. Other types of flip-flops can be constructed by using the D flip-flop and external logic. Two flip-flops less widely used in the design of digital systems are the JK and T flip-flops.

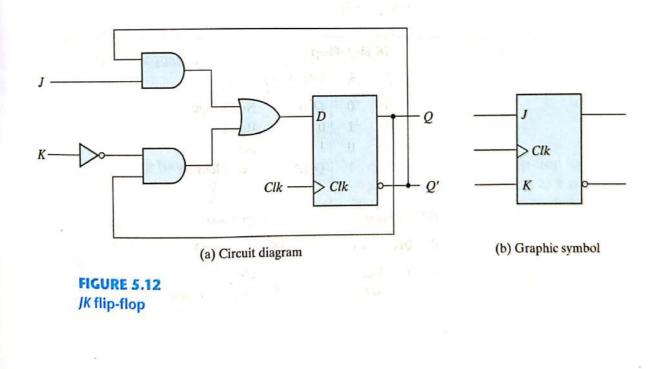

There are three operations that can be performed with a flip-flop: Set it to 1, reset it to 0, or complement its output. With only a single input, the D flip-flop can set or reset the output, depending on the value of the D input immediately before the clock transition. Synchronized by a clock signal, the JK flip-flop has two inputs and performs all three operations. The circuit diagram of a JK flip-flop constructed with a D flip-flop and gates is shown in Fig. 5.12(a). The J input sets the flip-flop to 1, the K input resets it to 0, and when both inputs are enabled, the output is complemented. This can be verified by investigating the circuit applied to the D input:

$$D = JQ' + K'Q$$

When J = 1 and K = 0, D = Q' + Q = 1, so the next clock edge sets the output to 1. When J = 0 and K = 1, D = 0, so the next clock edge resets the output to 0. When both J = K = 1 and D = Q' the next clock edge complements the output. When both J = K = 0 and D = Q, the clock edge leaves the output unchanged. The graphic symbol for the JK flip-flop is shown in Fig. 5.12(b). It is similar to the graphic symbol of the D flip-flop, except that now the inputs are marked J and K.

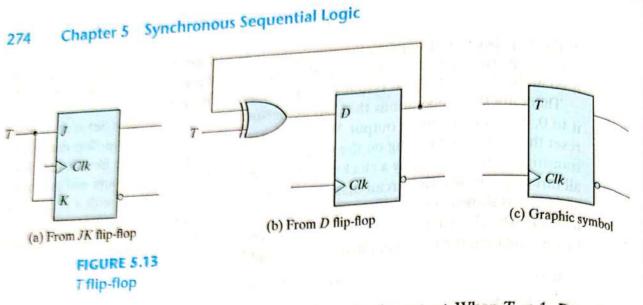

The T (toggle) flip-flop is a complementing flip-flop and can be obtained from a JK flip-flop when inputs J and K are tied together. This is shown in Fig. 5.13(a). When T = 0 (J = K = 0), a clock edge does not change the output. When T = 1 (J = K = 1), a clock edge complements the output. The complementing flip-flop is useful for designing binary counters.

The T flip-flop can be constructed with a D flip-flop and an exclusive-OR gate as shown in Fig. 5.13(b). The expression for the D input is

$$D = T \oplus Q = TQ' + T'Q$$

When T = 0, D = Q and there is no change in the output. When T = 1, D = Q' and when T = 0, D = Q and there is no enough or this flip-flop has a T symbol in the input, the output complements. The graphic symbol for this flip-flop has a T symbol in the input,

#### **Characteristic Tables**

A characteristic table defines the logical properties of a flip-flop by describing its operation in tabular form. The characteristic tables of three types of flip-flops are presented in Table 5.1. They define the next state (i.e., the state that results from a clock transition) as a function of the inputs and the present state. Q(t) refers to the present state (i.e., the state present prior to the application of a clock edge). Q(t + 1) is the next state one clock period later. Note that the clock edge input is not included in the characteristic table, but is implied to occur between times t and t + 1. Thus, Q(t) denotes the state of the flip-flop immediately before the clock edge, and Q(t + 1) denotes the state that results from the clock transition.

| JK    | Flip-l | Flop  |            |